JEDEC, the Solid State Technology Association, has announced the final DDR5 SDRAM specification. This new standard promises to deliver doubled memory bandwidth, alongside support for quadruple density dies, and greater power efficiency (1.1V Vdd). Additionally a DDR5 DIMM will operate in dual-channel mode all on its own, with two 40-bit fully independent sub-channels on the same module.

In brief, DDR5 will:

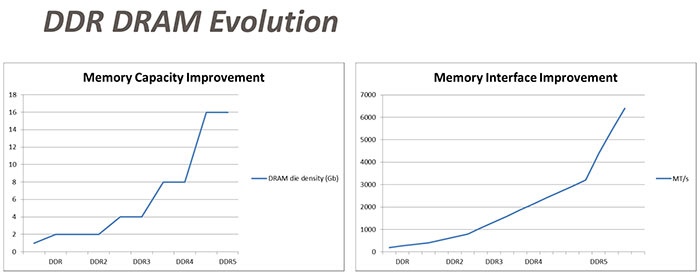

- Double the max die density to 64Gbit enabling DIMMs up to 2TB capacity when manufacturing catches up

- Offer a max standard data rate of 6.4Gbps - 50 per cent faster than the official 3.2Gbps max speed of DDR4. The first DDR5 modules are expected to launch at 4.8Gbps. Eventually DDR5 makers will likely bust the max 6.4Gbps figure.

- As semiconductor tech doesn't allow for much faster memory clocks DDR5 will use greater parallelism to increase performance. Thus DDR5 will offer two independent 32-bit data channels per DIMM (40 bit ECC) but the standard still requires DIMM pairs to be installed. Burst length for the channels is increased from 8 to 16 bytes.

- The operational voltage is lowered from 1.2V for DDR4 to 1.1V.

- Voltage regulation for memory will be removed from motherboards to these DIMMs. Using this methodology your motherboard doesn't need to be over-specced for a maxed out memory config. However, it remains to be seen if the transfer in costs works out for consumers.

- It will keep the same 288 pin count as DDR4 but don't expect to be able to utilise them in old DDR4 sockets as the pinout configuration won't be the same, mainly due to the dual-channel on module design.

JEDEC says that end users should expect the first DDR5 packing devices in 12 to 18 months from now, so we are looking at H2 2021. Neither Intel nor AMD has officially announced platform support for DDR5 but it is still early days.

The JEDEC press release about the finalised DDR5 spec does include testimonials from the likes of Intel, Micron, Samsung, and SK hynix. The latter confirms that it has been working with partners on DDR5 ecosystems and is looking to secure mass production facilities for the second half of this year. Meanwhile Micron has announced its DDR5 Technology Enablement Program.