Imagination Technologies says that its MIPS Warrior CPUs are gaining momentum as it gets more design wins and businesses see and experience them in action. Warrior CPUs range from high end processors to embedded SoCs and are increasingly found in shipping products. Unique features such as hardware multithreading, OmniShield multi-domain security, and others, are key to MIPS Warrior design wins, say Imagination Tech.

To maintain business momentum and address growing demand three new MIPS Warrior CPUs are being introduced; the high performance 64-bit P-class MIPS P6600 CPU and the performance-embedded 32-bit M-class M6200 and M6250 solutions.

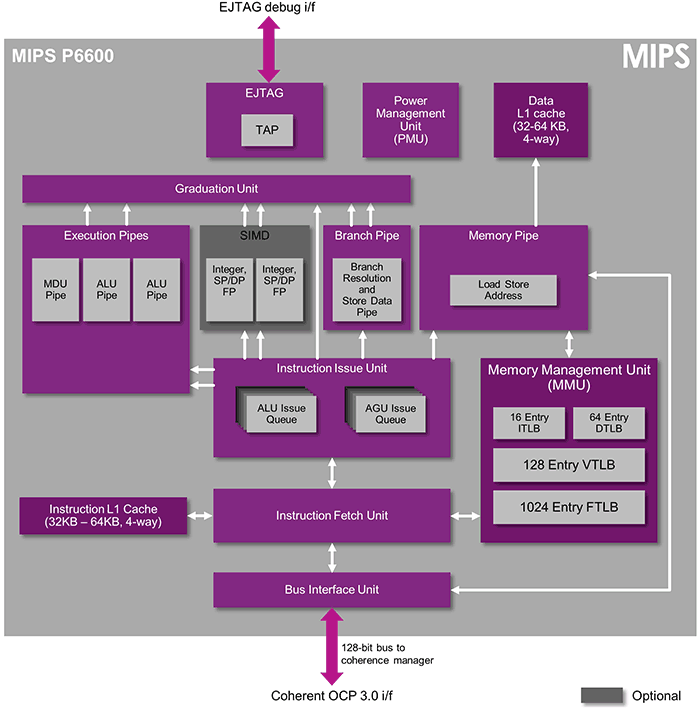

MIPS P6600

The MIPS P6600 CPU offers a straightforward upgrade to customers looking for a high-performance, 64-bit P-class Warrior CPU (it is an evolution of the 32-bit P5600 CPU). It implements the MIPS64 Release 6 architecture and delivers peak performance whilst minimising chip size and power consumption. Imagination foresees its deployment in mobile, home entertainment, networking, and HPC, plus industrial and embedded computer solutions. This new chip has already been licensed for applications including high-performance computing and advanced image and vision systems.

Users benefit from "a clear-cut boost in real-world workloads," thanks to best-in-class branch prediction and MIPS' load/store instruction bonding mechanism. The chip supports full hardware virtualization and enhanced security features. System designers can use the new P-class Warrior CPU in configurations that range from single to hexacore clusters.

MIPS P6600 key features

- High-performance 64-bit MIPS Warrior CPU based on a 16-stage multi-issue Out of Order (OoO) pipeline implementation, delivering outstanding computational throughput and area efficiency

- Integrated compiler-friendly 128-bit MIPS SIMD Architecture (MSA) support for efficient parallel processing of vector operations in multimedia applications

- Sophisticated branch prediction with fully associative Level 1 BTB (branch target buffer) and an improved Level 2 cache sub-system

- Full hardware virtualization support and Imagination’s OmniShield technologies for enhanced security and reliability in a wide range of applications

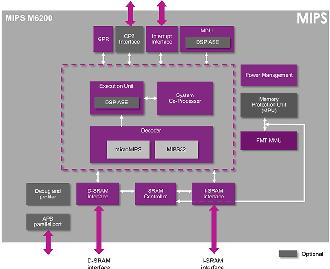

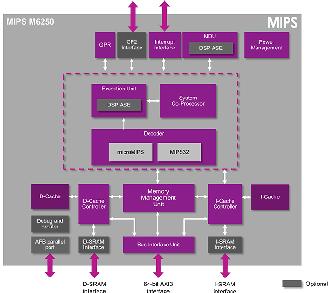

MIPS M6200 and M6250

Joining Imagination's popular M-class family are the MIPS M6200 and M6250, providing a broader M-class roadmap for "high-performance deeply embedded designs". Imagination foresees these processors being deployed in wired/wireless modems, GPU supervisor processors, flash and SSD controllers, industrial and motor control, advanced voice processing and others.

The MIPS M6200 and M6250 are based upon the MIPS32 Release 6 architecture and are capable of operating at 30 per cent higher frequencies than other members of the family. Looking at their differences the M6200 is tailored for devices that run real-time operating systems while the M6250 is designed for devices requiring Linux capabilities.

|

|

MIPS M6200 MCU & M6250 MPU key features

- Low-power, compact 32-bit CPUs based on a 6-stage pipeline implementation, enabling 30% higher frequencies versus the MIPS microAptiv CPU for similar implementations

- Integrated DSP and SIMD functionality to address signal processing requirements of such applications as industrial/motor control, voice processing and more

- Support for microMIPS r6 Instruction Set Architecture (ISA) for superior code compression and reduced memory footprint

- Data integrity features, including ECC and parity protection

- AMBA APB debug interface enabling JTAG, multi-core and mixed core debugging

- M6200 MCU:

Includes a memory controller for tightly coupled 64-bit Instruction/Data SRAM

A memory protection unit enables program/data security - M6250 MPU:

Includes a memory controller for Instruction/Data L1 cache and optional tightly coupled ScratchPad RAMs (SPRAMs)

A Memory Management Unit (MMU) supports virtual memory, enabling full support for Linux and other high level operating systems

40-bit eXtended Physical Addressing (XPA) support

AMBA AXI3 Bus Interface Unit

You can read more about the new MIPS processors, and the Release 6 architecture behind the designs, in Imagination's blog post about the new Warrior CPUs. The M6200, M6250 and P6600 are all available now, just contact info@imgtec.com.