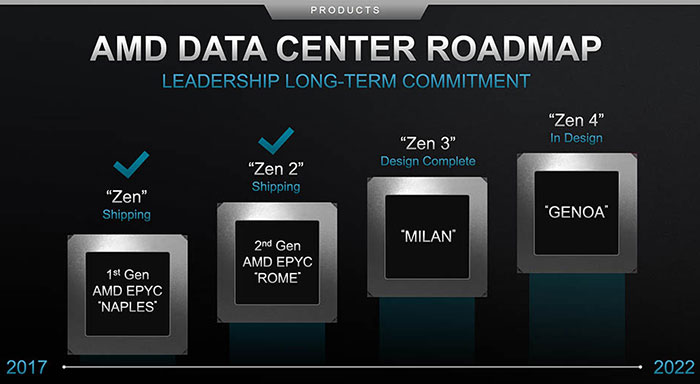

AMD took to the stage at the HPC-AI Advisory Council UK conference recently with a presentation about its upcoming architectures and processors for servers, data centres and similar high performance computing platforms. The presentation was only a month or so after the launch of the Epyc 2 Rome line of processors - a line which won solid industry support from the start, with important new customers such as Google and Twitter, and which will be taking chunks out of Intel's market share as I write.

At the conference in Leicester, AMD shared some new details and slides about its Zen 3 and Zen 4 architectures and some new info about the next-gen Epyc Milan and Epyc Genoa processors. Tom's Hardware notes that the presentation was shared on YouTube but after the first reports broke of its content, it has been "taken down in rather quick fashion," probably due to content being a little beyond the public knowledge curve.

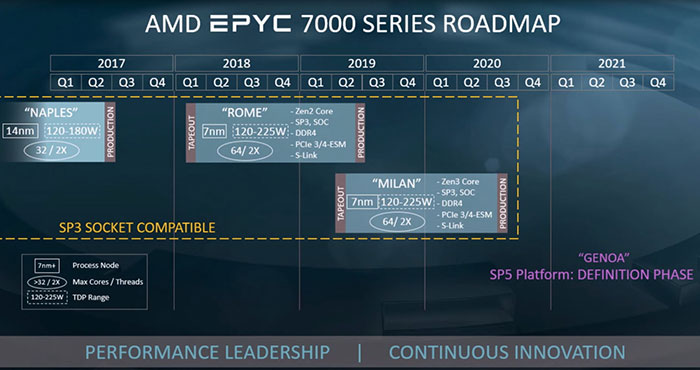

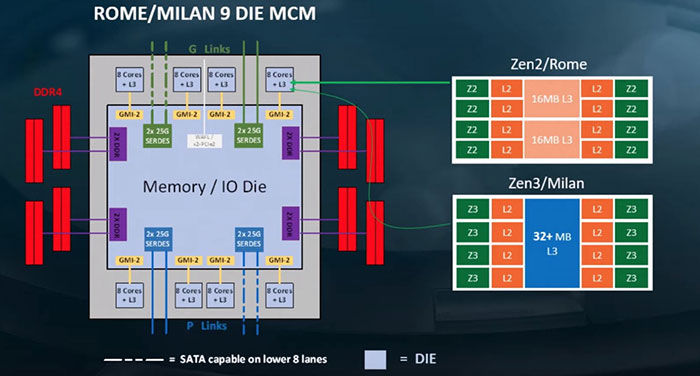

From the slides shared it look like Epyc Milan is already taped out (Q2 2019), and it is already sampling them with its important customers. This processor shares many qualities with Epyc Rome on the surface of things. In the roadmap graphics you can see the only real change is to Zen3 cores. However, it is worth highlighting the processor will use the Zen 3 architecture, with unified 32MB L3 cache, so there will be some uplifts from that, as well as the move to TSMC's 7nm+ node. There was a rumour that AMD was intending to run up to 4 threads per core, but this roadmap clearly dispels that.

Moving along approximately another year, we see that the (likely Zen 4 architecture) Epyc Genoa will be AMD's newest hope for the server / data centre markets. Genoa won't use the SP3 platform, but will be the first of AMD's SP5 platform chips. At this time, in its 'definition phase', it looks set to be built on an advanced 7nm node, with up to 32 x2 SMT cores, and a TDP between 120 - 225W. At the presentation it was said that Genoa will support "new memory" which probably means DDR5, and it is also thought that AMD will include PCIe 5.0 connectivity.

Though the above is all Epyc processor centric info, similar advancements will be on the way to consumer desktop, mobile and HEDT in not too dissimilar timescales.