While JEDEC, the memory standards body, has yet to formally outline the HBM3 memory standard, SK hynix has been busy developing what it thinks HBM3 memory will be. The firm should have a pretty good idea about this, as it is a major JEDEC member and instrumental in drafting many previous standards.

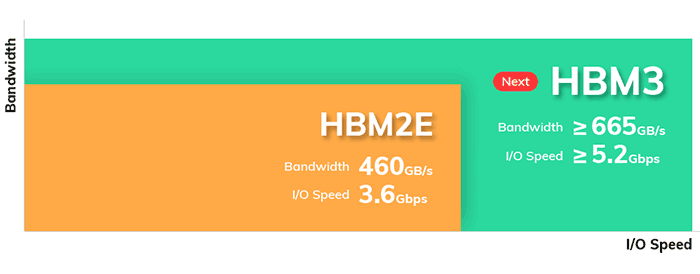

On a product page outlining its 16Gb HBM2E, SK hynix has provided some insight into the attractions of HBM3, the next HBM standard. It says that SK hynix HBM3 is currently under development and "will be capable of processing more than 665GB of data per second at 5.2Gbps in I/O speed". In the chart below, poached from the aforementioned product page, you can clearly see the progress that HBM3 represents.

Above you can see that HBM3 builds upon HBM2E, with its ≥665GB/s bandwidth – compared to 460GB/s bandwidth for HBM2E, and its ≥5.2Gbps I/O speed - compared to 3.6Gbps for HMB2E. It is interesting to see that SK hynix already looks confident of achieving greater performance figures.

Tom's Hardware notes that contemporary ultra-high-end compute GPUs or FPGAs use 4-6 HBM2E memory stacks for 1.84-2.76TB/s of bandwidth but with HBM3 in place they could potentially be upgraded to as much as 3.99TB/s.

There are expectations that SK hynix will leverage DBI Ultra 2.5D/3D hybrid bonding interconnect technology from Xperi Corp for its latest HBM solutions. This tech supports up to a million interconnects per square millimetre and allows for stacks 16 high – for great density potential – so you could see very high memory densities or 2.5D or 3D solutions with built-in HBM3.

We don't have any information about when HBM3 might become available or be integrated into components / devices.