The PCIe 5.0 specification has been completed and released to members, announced the PCI-SIG. Again we see with this revision, a doubling of peak bandwidth facilitated by the new interconnect technology. It has taken the PCI-SIG and its members less than 18 months to complete the PCIe 5.0 spec. PCI-SIG members can receive exclusive access to PCI-SIG Compliance Workshops and Developers Conferences, participation in specification revisions and more - and some members are already developing their first PCIe 5.0 solutions. Members include the likes of AMD, Intel and Nvidia.

The PCI-SIG feels some pressure to advance as "new data-intensive applications are driving demand for unprecedented levels of performance," noted Al Yanes, PCI-SIG Chairman and President. "The PCIe architecture will continue to stand as the defacto standard for high performance I/O for the foreseeable future," he pledged.

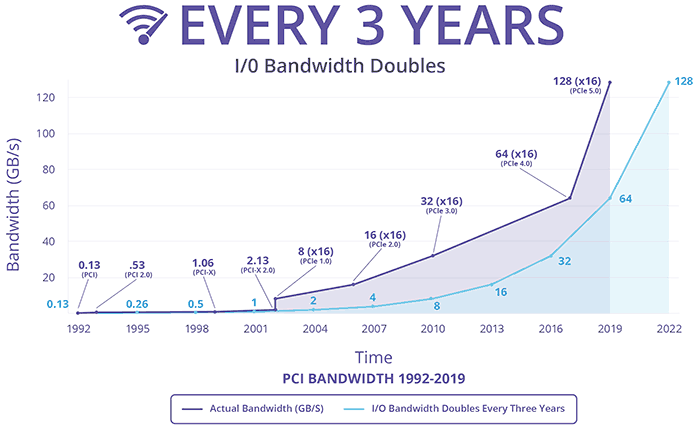

As you can see clearly illustrated by the chart below, PCIe solutions have historically been able to double the peak bandwidth at an impressive rate. The latest PCIe 5.0 spec, with peak bandwidth of up to 128GB/s via x16 configuration keeps the spec development well ahead of the I/O bandwidth doubling every three years envelope.

PCIe 5.0 specification highlights

- Delivers 32GT/s raw bit rate and up to 128GB/s via x16 configuration

- Leverages and adds to the PCIe 4.0 specification and its support for higher speeds via extended tags and credits

- Implements electrical changes to improve signal integrity and mechanical performance of connectors

- Includes new backwards compatible CEM connector targeted for add-in cards

- Maintains backwards compatibility with PCIe 4.0, 3.x, 2.x and 1.x

We've only just begun to see consumer devices with the PCIe 4.0 spec, most notably due to AMD's latest chipset the X570. However, it looks like there won't be such a big gap until PCIe 5.0 products start to proliferate. Already we see that Silicon Labs has shown off its first PCIe 5.0 clocks and buffers.