Slides said to be from an official MediaTek presentation have leaked onto the web. The slides appear to show technical details of the "industry's first Tri-Cluster CPU architecture," which is the foundation of the MediaTek Helio X20 SoC. We also get to see a slide boasting that the new 10-core chip can achieve a score of 70,000 in the AnTuTu mobile benchmark.

A Weibo user published slides today putting MediaTek's upcoming MT6797 SoC, the first of the Helio X20 range, under the spotlight. The new deca-core processor is boasted to offer a 40 per cent improvement in benchmarks over previous Helio X10 parts, as evidenced by an AnTuTu benchmark score of 70,000. It also offers an interesting alternative to the traditional ARM big.LITTLE processor core configurations already out there.

big - MedIUM – LITTLE?

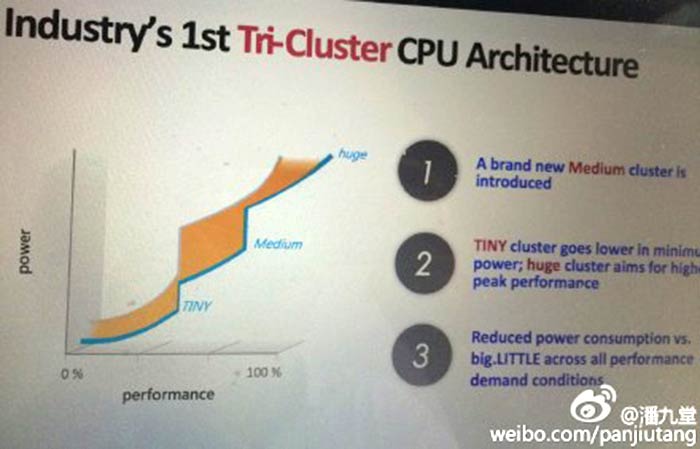

The Tri-Cluster CPU concept draws a parallel from the automotive industry, according to the slides. "More gears gives better fuel efficiency across different road conditions," one of the slides informs us. Thus MediaTek has augmented the usual ARM 'big.LITTLE' clusters with a 'medium' component. MediaTek calls the Tri-Cluster arrangement TINY-Medium-huge.

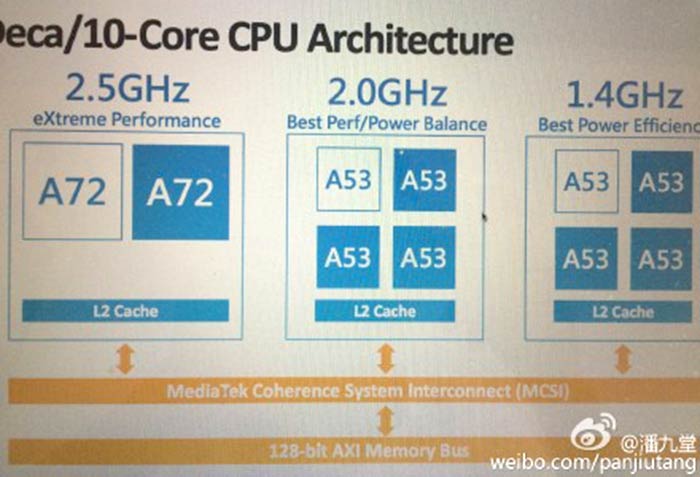

Within the Tri-Cluster arrangement the MT6797 provides two 2.5GHz A72 cores offering 'extreme performance', these are partnered by a quartet of 2.0GHz A53 cores providing 'best performance/power balance'. Completing the Tri-Cluster and offering the 'best power efficiency' we have four 1.4GHz A53 cores. All three parts of the 'TINY-Medium-huge' arrangement have their own L2 cache and are connected via the MediaTek coherence system interconnect (MCSI) and a 128-bit AXI memory bus.

The above arrangement offers "reduced power consumption vs ARM big.LITTLE across all performance demand conditions," says MediaTek.

According to other reports the MediaTek MT6797 SoC will be produced using TSMC's 20nm process and be equipped with an LTE-A/Cat.6 radio. The deca-core processor is expected to hit mass production in July and will probably begin to appear in devices sometime in Q4 this year.