Intel is at the International Supercomputing Conference in Leipzig and made use of the occasion to announce its Next-Generation Xeon Phi Processor with Integrated Intel Omni Scale Fabric.

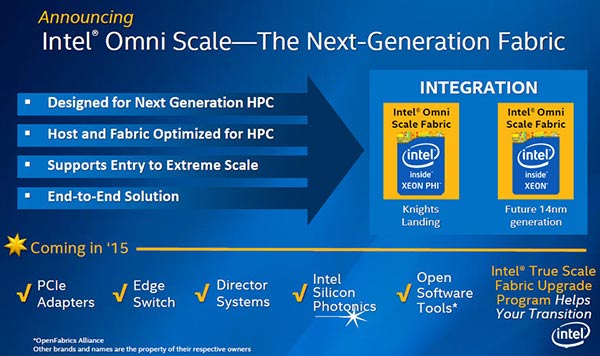

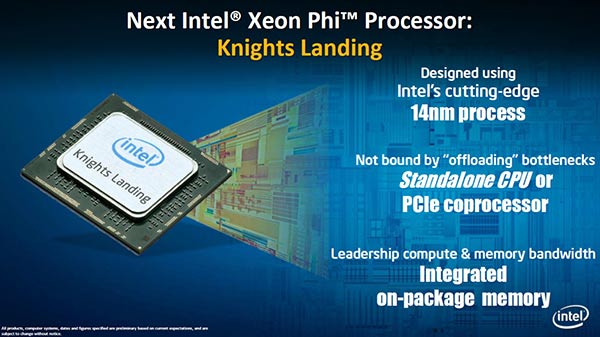

The Xeon Phi many-core processor, code named 'Knight's Landing', includes a new interconnect technology which eliminates some troublesome bottlenecks which were hindering the progress to the goal of exascale computing. The 'fabric' within the chip helps address the memory and I/O performance challenges which face the world of high-performance computing (HPC).

Unlike its predecessor Knights Landing will be available as a standalone processor directly on a motherboard. This helps remove the PCI-e "programming complexities and bandwidth bottlenecks". The chip will also include up to 16GB of high-bandwidth, on-package memory at launch, said to deliver "five times better bandwidth compared to DDR4 memory, five times better energy efficiency and three times more density than current GDDR-based memory". Intel will also be supplying the Knights Landing and Intel Omni Scale Fabric controllers as PCIe-based add-on cards for system makers who prefer.

The current generation of Intel Xeon processors and Intel Xeon Phi coprocessors power the top-rated system in the world, the 'Milky Way 2' in China. The new Knights Landing and Omni Scale Fabric should help push things further. The three trillion double precision floating point operations per second (3 teraflops) in a single processor socket provided by the next generation Xeon Phi is complemented by it offering three times the single threaded performance of the current generation.

Intel says that a Knight's Landing processor is powered by more than 60 HPC-enhanced Silvermont architecture-based cores. Used as a standalone processor it will support DDR4 system memory. Due to its motherboard socketed form factor option it is expected to be used more broadly than its predecessor was, in workstations for example.

Expect to see Knight's Landing in HPC systems from H2 2015.