This is a guest blog by Chris Turner, Director of Advanced Technology Marketing for ARM’s CPU Group. The views expressed in this blog are his and his alone. We invited Chris to share some of his thoughts on Cortex-R8, the industry's most powerful real-time processor and a precursor to 5G modems.

Between now and 2022, cellular speeds are going to soar to as high as 10Gbps as new 5G technologies hit the marketplace. But the path to those achievements - up from the several hundreds of megabits per second with LTE and LTE-Advanced (4G) technologies - is a challenging one for mobile SoC developers.

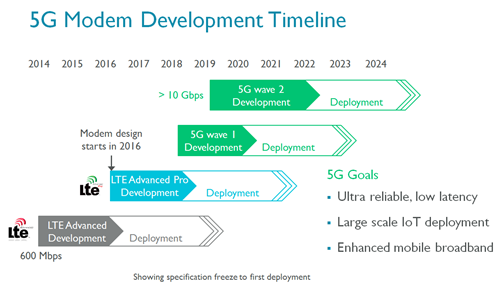

Consider the time frames:

The next, and possibly final, fourth-generation standard, LTE-Advanced Pro, is upon us, with modem designs beginning this spring. The first wave of 5G modems is expected to be designed in a 2018-19 timeframe - so the clock is ticking. There will be even more carrier frequencies, multiple antenna arrays and new features for broadcasting, the IoT, emergency services and the like all contributing to increasing workload and feature set requirements for the modem processor.

So, given the tight timeframes and challenging design considerations, where do silicon providers sit right now?

The bars in the image above show the period when silicon vendors start designing and testing their chips up until their market introduction in a mobile phone. The service roll-out happens after that. You can see we anticipate the second wave of 5G to be a more challenging when new air interfaces using very high millimeter-wave frequencies have to be developed.

Complexities abound

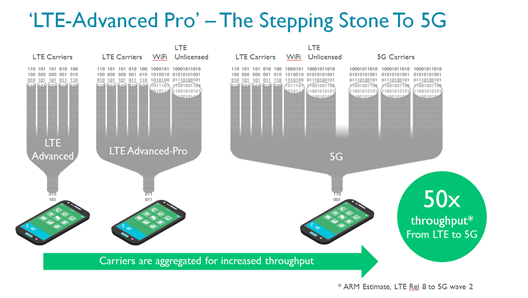

The next generation LTE-Advanced Pro standard brings both WiFi and also new unlicensed-band cellular technology together with existing LTE-Advanced in the same modem. This creates a further substantial increase in the modem processing tasks.

Then, with 5G, even more carriers are planned. There will be higher data rates, multi-dimensional antennas, direct phone-to-phone services, mission-critical services designed for first responders, low-latency services for vehicles and highways and new narrow-band communications designed for the IoT and other capabilities for the 2020s.

Carrier aggregation is a key feature of these new cellular wireless standards. It allows mobile network operators to send and receive data over a number of different radio frequencies, thus making most efficient use of their spectrum allocation. However, implementing this technology, especially in a smartphone, is challenging as the modem has to manage all the carriers simultaneously.

This technological evolution is changing the game for processors that, up until now, have served in 3G and 4G modems admirably.

With LTE-Advanced Pro and onward to 5G, the increasing software workloads in the protocol stack layers and new data-scheduling complexities require an evolved real-time multicore processor to complement the modem’s signal-processing engines and various dedicated hardware accelerators for security, compression and the like.

In addition, modem designers are asking for even more layer-1 scheduling activities to be managed by software in the processor instead of dedicated hardware. This allows more flexibility when switching between all the different communication standards.

Anticipating these design demands, ARM has introduced the Cortex-R8 to support this next set of LTE-Advanced Pro modems and the initial 5G design cycles. It is a very fast processor and can deliver over 15,000 Dhrystone MIPS from a quad-core configuration on a 28nm or 16nm silicon process.

Like ARM’s top-line application processors, the new Cortex-R8 can execute instructions out of order. This can be key to success in real-time applications like modems because it enables the processor to continue execution whilst outstanding memory or peripheral device transactions are in flight.

The Cortex-R8 scales in terms of size and capability. Chip designers can optimize it for their application by selecting configurations from one-to-four CPU cores, L1 memory sizes, a choice of bus interfaces, error handling features, and so on. Also, once a chip is running, the software can power cores up and down depending on workload.

Memory management

The Cortex-R8 takes interrupts into its pipeline as quickly as possible and then services them with code and data stored in a tightly-coupled memory (TCM), thus avoiding the longer and non-deterministic latency cycles you get when fetching interrupt service routines into the cached memory system. Cortex-R8 supports eight times as much TCM than the R7 did, all the way up to 8MB in its quad-core configuration.

Why is the Cortex-R8 is attractive to system on chip designers? Firstly, there is a lot of software already out there, for example modem protocol stacks and drivers going all the way back to 2G, then GPRS, HSPA, etc., followed by first-generation LTE.

All this software and the associated electronic system-level design, simulation and verification tools and know-how represents a huge investment for the modem design teams at our silicon partners, so that investment is maintained by Cortex-R8, offering them scalability and forward compatibility.

By the way, a lot of that ESL design support also comes from ARM, including the Cortex-R8 C-compiler, instruction and data trace and debug, fast models for software development in advance of silicon and cycle-accurate models for ARM’s partners' SoC design, development and verification activities.

In addition, the complexity of this software has increased dramatically and the rest of the modem hardware is also complex. The Cortex-R8’s quad-core CPU and coherent memory system allows software execution to be parallelized across the four cores and various interfaces into the modem hardware can be used to achieve the best performing and lowest power overall design.

Another characteristic of all the ARM Cortex real-time processors is that they are designed to minimize latency for memory reads and writes using a protected memory system. This is different to the virtual memory system that is needed for a high-level OS like Linux or Android and, for the Cortex-R processors running a real-time operating system, it is key to their ability to start responding to hard real-time events in less than a microsecond.

With four cores to spread the software over, there are more advantages as it’s less likely that silicon implementation techniques like voltage overdrive or very high frequency operation using low threshold transistors will be needed. That of course can save a considerable amount of power.

Testing with silicon partners’ software has already demonstrated that the Cortex-R8’s aggregate multi-core performance up to 28,000 CoreMarks is more than sufficient for the next set of LTE-Advanced Pro and first 5G modem designs.

For more information please visit our Cortex-R technology page.