Gracemont flies into the mix

Sharing the same ISA as Golden Cove, Gracemont is not entirely new technology as it uses the guts of the existing Tremont Atom architecture and improves upon it in a few ways.

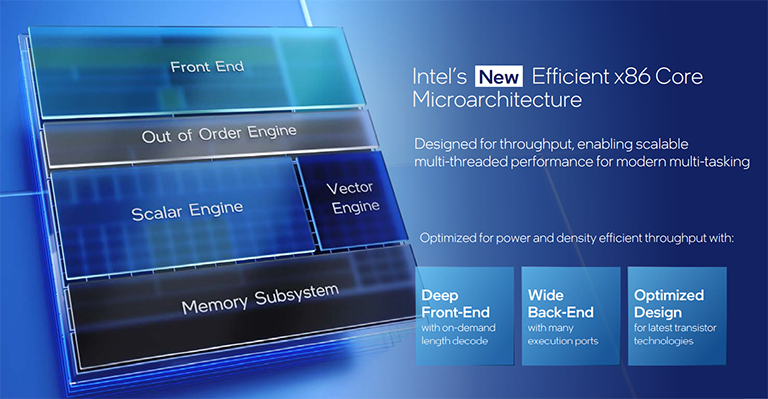

Intel doubles the instruction cache compared to Tremont. Like its predecessor it delivers six instructions per clock cycle and has a massive 17 execution ports for parallel processing. Other than the headline specs highlighted in the above slide, the front-end of the architecture is interesting because it features dual 3-wide decoders for six instructions per clock cycle. Each decoder pulls instructions from the L1 cache, but unlike the bigger Performance core, it doesn't feature any form of op-cache for recycling previously-decoded instructions. Gracemont, however, running a side-by-side design, can decode instructions in parallel, which may help mask some latency if there is, on occasion, no branch. Put simply, Gracemont is not a shrunken-down Golden Cove on a reduced voltage plane.

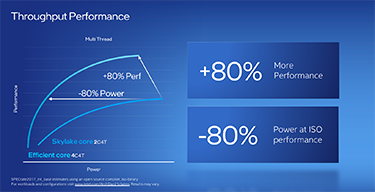

The burning question is why Intel would integrate small cores alongside large ones? Doesn't it make more sense to persist with the status quo and run more high-performance cores than the previous generation? The answer is nebulous. Intel says the more power-efficient Gracemont cores work very well in TDP-constrained environments such as mobile. That makes sense, but is that still true for desktop and server, where TDP is less of an issue. And if more low-power cores are better than a few high-performance ones, why doesn't Alder Lake use, say, 32 or 64 Gracemont alone?

Intel believes pairing, for example, eight hyperthreaded Golden Cove cores with eight Gracemont is a better overall fit than having 10 Golden Cove alone, as using small cores makes sense for background tasks and for extra multi-thread muscle as and when needed. We're not convinced until the benchmark numbers are in, and while mobile specialist Arm has been plying the big.LITTLE design ethos for years - it makes a lot more sense in mobile - does it work as well at 125W?

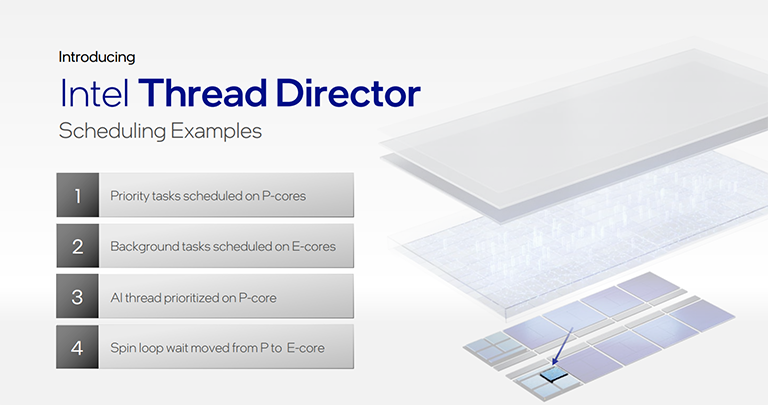

Then there's the issue of how to apportion the correct threads on the right processors, which is a problem that does not arise on a same-core design. Operating systems can do only so much to facilitate correct thread dispatch and if the scheduler messes up on a big/small design like this, performance is sure to plummet.

This is why resource has been spent in developing what the company terms Intel Thread Director. Dynamic and autonomous to the operating system, hardware-based Thread Director technology monitors the exact instruction mix, the current state of each core (big or small), and various bits of telemetry... all in a bid to move the right thread on to the right core. This information is fed to the OS so that it can make better scheduling decisions. Gaming and multi-threaded applications will run on the Performance cores whilst stuff like email synching or browsing map on to Efficient cores.

That's the easy stuff. What happens when all Performance cores are busy and another thread requiring top-bin performance comes along - AI processing, for example. In this scenario, Thread Director advises the OS to move one of the existing Performance threads over to the Efficient cores and replace it with this even-higher-performance thread. In other words, Thread Director is said to make intelligent decisions on the absolute needs of each thread - relative performance ordering - and guide the OS scheduler down the right path.

Intel says it is working with Microsoft to have Thread Director fully operational in Windows 11. That's all well and good, but the same smarts won't immediately be available for Windows 10, leaving the OS scheduler to handle the apportioning work. How this is likely to play out in the field is yet another unknown.

Outside of hard-nosed architecture, we know Alder Lake will require a 600-series motherboard based on the desktop LGA 1700 socket. The top part will feature eight hyperthreaded Performance cores and eight Efficient cores, for a total of 24-thread processing. That is still behind the 16C32T topology of the latest AMD Ryzens, of course. We're pretty sure the best Alder Lake will still be behind the premier Ryzen in multi-threaded tasks as the latter simply has more muscle at its disposal. 32 Zen 3 threads have to be better than 16 Golden Cove and eight Gracemont, right?

The external memory controller can handle both DDR4 or brand-new DDR5 (not both on the same board) so manufacturers will have to choose their offerings carefully. On the desktop, Alder Lake up to 16 PCIe 5 lanes and a number of PCIe 4/3, though the exact number and routing is unknown.

Keeping all this potential bandwidth is play is a new interconnect system as DMI simply does not have the chops. Intel quotes some heady numbers on this front, but as with many things, more will be known closer to the late-October launch.

On an architectural level, we can make pretty solid guesses on the probable performance of the Golden Cove Performance cores. What's almost impossible to ascertain is how the Gracemont Efficient cores will skew full-on processing, especially in a desktop environment.

There are more questions than answers at this point in time. Intel is taking a calculated risk in moving to a hybrid-core model for this generation and the next. We're not convinced it'll work out well in the high-end desktop space, primarily due to having a thread deficit against AMD. What do you think? Does Intel's Alder Lake stoke excitement or is it a damp squib? Let us know your thoughts in the forums.