In particular, those of special note include updates to its process technology roadmap, offering crumbs of new information on the soon-to-be introduced, mobile-oriented Silverthorne CPU and two-billion transistor, quad-core Itanium 2 processor, Tukwila.

Silverthorne

At IDFs (Intel Developer Forums) in the past year, Intel has been keen to harness the burgeoning popularity of mobile Internet devices (MIDs) and ultra-mobile PCs (UMPCs) - usually all-in-one PCs with five- to seven-inch screens - and has put forward its Menlow proposition as the platform of choice for a wide range of OEMs now building such devices, usurping the current McCaslin platform offering.Menlow packs in the Poulsbo chipset and all-new 45nm-based Silverthorne CPU, and details of the latter have been sketchy at best.

Intel has confirmed that the single-core Silverthorne is a grounds-up design based on an IA (Intel Architecture) micro-architecture. Pulling between 0.6W-2W under load, the power-efficient design is based on a dual-issue in-order pipeline that includes HyperThreading - so thread parallelism in a fully moble design. It's also fully Core 2 Duo ISA compatible, too, and clock-for-clock performance is reckoned to be on a par with the first-generation Centrino processor, codenamed Banias.

Silverthorne will be <25mm and carry 47M transistors, we learned.

Designed with battery life very much to the fore, it's equipped with far greater granular control over power and speeds, and can switch to and from deep power-down mode (C6) in just 100ms. Silverthorne is merely the CPU and not a system-on-a-chip, though, and it's worth repeating that a discrete memory-controller and supporting chipset (Poulsbo), accessed via a traditional FSB, are required to complete the platform.

Intel commented that a number of nifty power-saving technologies have been further designed in, but wouldn't go into greater detail on this count.

Menlow-based devices will be released as soon as Q2 2008, apparently, but we'll have to wait until the next evolution of Intel's low-power processing, Moorestown, before we see smaller-than-iPhone devices with Intel Inside, we reckon.

Tukwila

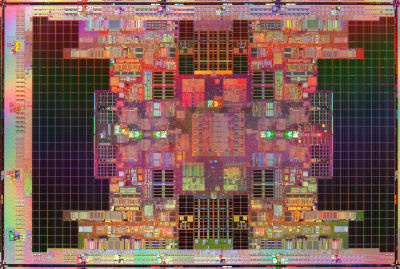

Tukwila is the next iteration of Intel's Itanium (2) processor, designed to supersede the incumbent dual-core Montvale.Whilst the guts of the 65nm processor are much the same as 90nm Montvale's, Tukwila packs in four cores with SMT processing on top, so parallel eight-thread execution.

Clocked in at up to 2GHz on launch, Tukwila will ship with 30MiB of on-chip cache, utilise dual integrated memory-controllers, and, getting rid of the front-side bus, will be equipped with QuickPath point-to-point interconnects between multi-socketed processors and the system. Conjecturing somewhat, link performance is reckoned to be around 32GB/s.

The beefy processor, used in very high-end server systems, will be comprised of two-billion - yes, two-thousand million - transistors and will offer up to 2x the current Montvale's 9100's performance. It will ship with a higher TDP of 130W, however.

That's the CPU news done; more on phase-change memory and tera-scale technology tomorrow.