Earlier in December Intel introduced its all new Intel Pentium Silver and Intel Celeron processors. Six new processors were released to systems and device makers and we should see the first fruits bearing these SoCs soon, in Q1 2018. Intel's new Goldmont Plus microarchitecture was the basis for its recent Gemini Lake platform launch and, as a reminder, it replaced the Goldmont microarchitecture that powered Apollo Lake chips.

At the time of the Pentium Silver launch we got a broad brush strokes rundown of the new processor ranges' attractions. They sported perkier performance, better modern graphical capabilities, improved networking, and were said to be very energy efficient. However, we didn't learn much in the way of technicalities on what was different from Apollo Lake.

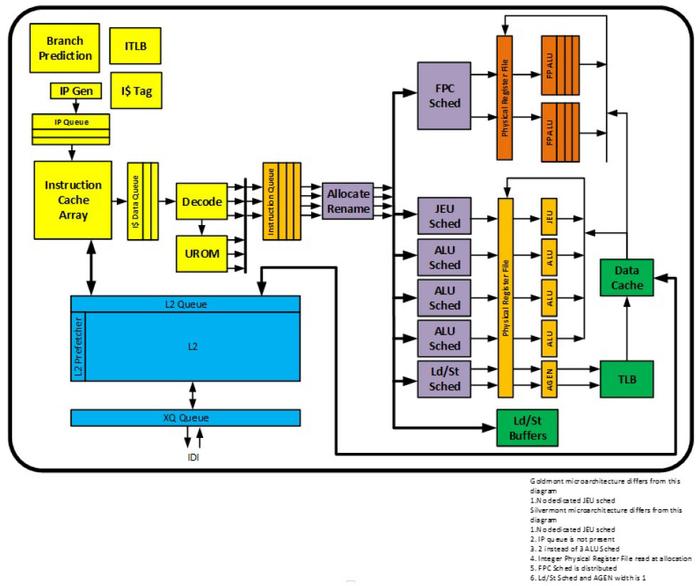

Now Intel has shared some further architectural information regarding the Goldmont Plus microarchitecture. In a PDF reference manual aimed at developers (link, go to chapter 16) Intel shares a list of architectural enhancements over the original Goldmont microarchitecture and a CPU diagram. Below is the full list of enhancements present taken directly from the PDF:

- Widen previous generation Atom processor back-end pipeline to 4-wide allocation to 4-wide retire, while maintaining 3-wide fetch and decode pipeline.

- Enhanced branch prediction unit.

- 64KB shared second level pre-decode cache (16KB in Goldmont microarchitecture).

- Larger reservation station and ROB entries to support large out-of-order window.

- Wider integer execution unit. New dedicated JEU port with support for faster branch redirection.

- Radix-1024 floating point divider for fast scalar/packed single, double and extended precision floating point divides.

- Improved AES-NI instruction latency and throughput.

- Larger load and store buffers. Improved store-to-load forwarding latency store data from register.

- Shared instruction and data second level TLB. Paging Cache Enhancements (PxE/ePxE caches).

- Modular system design with four cores sharing up to 4MB L2 cache.

- Support for Read Processor ID (RDP) new instruction.

You can see above that the new processors have a wider back end pipeline, an enhanced branch prediction unit, a much larger L2 precode cache, and new addition of a dedicated JEU (Jump Execution Unit). Additionally AES instruction latency and throughput have both improved and an increased L2 cache (from 512KB per core to 1MB per core) is present.

click to zoom image

Hopefully the performance uplift provided in the transition from Silvermont to Goldmont based systems is repeated with Goldmont Plus, to deliver increasingly attractive entry level priced, low power systems for mobile and desktop use.