On Tuesday Intel presented at its Technology and Manufacturing Day in San Francisco. The show streamed live to analysts, investors and media worldwide and Intel used it as a showcase for its new tech initiatives. As well as deeper tech presentations by the likes of Mark Bohr, Stacy Smith, Kaizad Mistry, and other Intel luminaries, it published the triumphant 'Leading at the Edge' video, below.

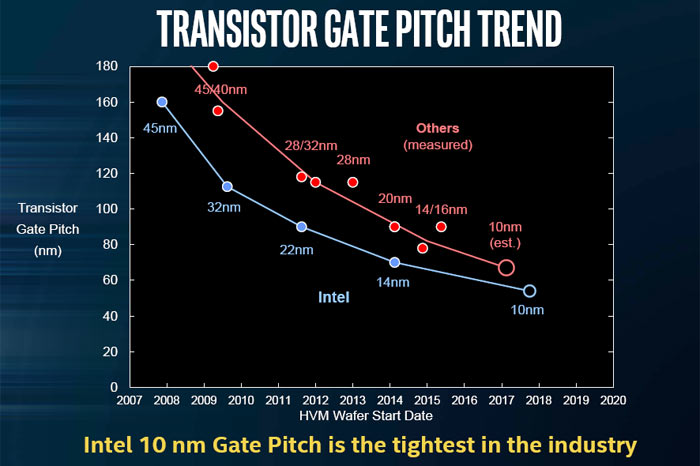

Amongst the press materials from the day there's an interesting PDF fact-sheet which seeks to explain why Intel's 10nm technology is "estimated to be a full generation ahead of other 10nm technologies". This document can be supplemented by a PDF press deck from Kaizad Mistry, the CVP of Technology and Manufacturing Group and Co-Director of Logic Technology Development at Intel.

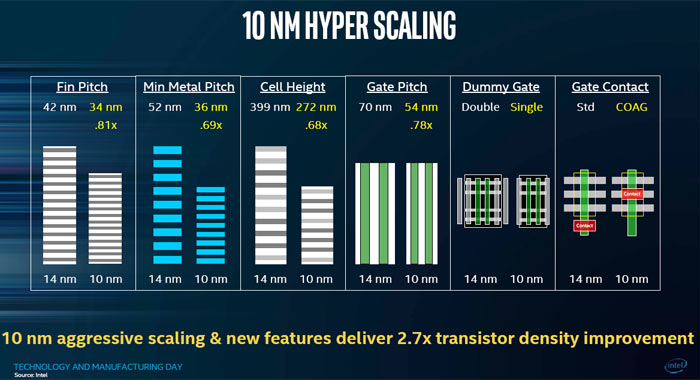

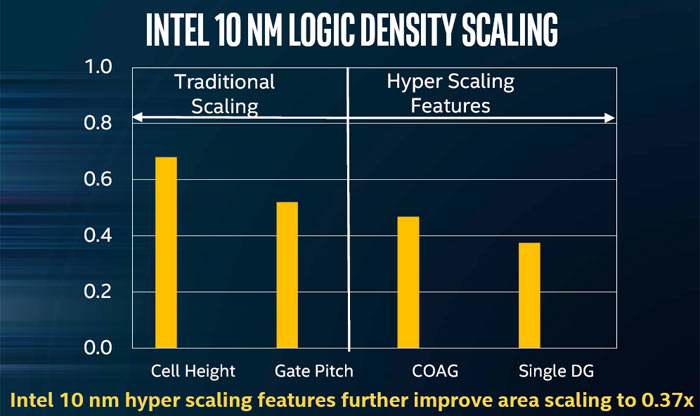

Much of Intel's claimed 10nm process advantage is down to the use of library height scaling and 'hyper scaling'. Scale reduction technology allows Intel to continue the benefits of Moore’s Law economics "by delivering transistors that are smaller and have lower cost-per-transistor". It can do this even though the transition between process nodes appears to have slowed down.

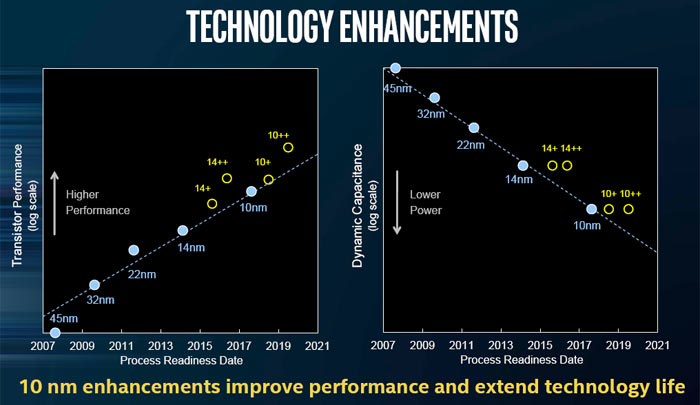

Thanks to the new scaling tech the minimum gate pitch of Intel's 10nm process shrinks from 70nm to 54nm and the minimum metal pitch shrinks from 52nm to 36nm. The logic transistor density of a new Intel 10nm chip can thus be 2.7x higher than Intel’s previous 14nm technology. In knock-on performance benefits it can provide a 25 per cent uplift at 45 per cent power reduction compared to 14nm. Furthermore, Intel says that its refined 10nm++ process "boosts the performance an additional 15 per cent while reducing power by another 30 per cent."

Intel has managed to scale its 10nm process so well thanks to new library height scaling of fin pitch and metal pitch. Furthermore, behind the umbrella 'hyper scaling' term are two technologies, as follows:

- COAG (contact over active gate) - A process feature whereby the gate contact is stacked on top of the transistor gate rather than at its side. Intel has implemented COAG in its 10nm process – an industry first – thereby improving transistor density.

- SingleDG (single dummy gate) - A gate that isn’t part of a transistor, put on the edge of a logic cell, needed to isolate one cell from another. Traditional processes used two dummy gates per cell; Intel’s 10 nm process requires only a single dummy gate, thereby improving transistor density.

Intel plans to build its 10nm chips for three years before it gets around to deploying 7nm technology. Intel EVP of manufacturing, operations and sales, Stacy Smith, wrote in a blog post "We are always looking three generations - seven to nine years - ahead," before concluding that "Moore's Law is not ending at any time we can see ahead of us."