How it works

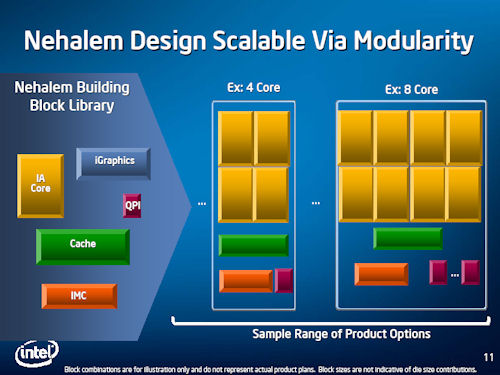

Smith also stressed that Nehalem was ’probably our most scalable and dynamic’ microarchitecture yet.

By dynamic, he was referring to the ability of the processor to adjust its power use depending on workload and by scalable he was talking about the modular design, which allows different products to be produced from the same die.

Nehalem's infrastructure, then, will use a building-block approach,

much like AMD's recently-disclosed APU

platform. Such an approach, Intel will claim, gives it the flexibility

to meet its customers' needs in a more-efficient manner.

Another feature Smith was keen to bring attention to was

two-way simultaneous hyper-threading. This not only allows each core to

deal

with two threads at a time, but is apparently very power efficient and

is

enhanced by the additional cache and memory bandwidth on offer.

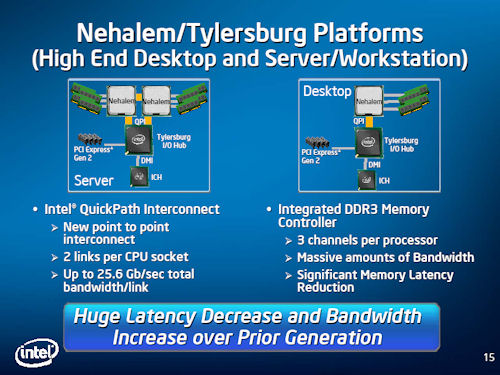

And here is a summary of the features of QPI and IMC.

Ultra-fast interconnects are a mainstay of the server and HPC space,

where data needs to be moved around quickly between CPUs in a

multi-socket platform.

Lastly, we got a confirmation of the next phase of

‘Tick-Tock’.

The Tick is the first 32nm product, which is a compaction of Nehalem,

is due to

go into production in 2009 and is codenamed Westmere.

The Tock is the second generation 32nm, which will feature

Advanced Vector Extensions - wider vectors for greater FLOP output and

optimised data-load algorithms. It is due in 2010 and is codenamed Sandy

Bridge.

N.B. While I attended the Intel press event and wrote most of this piece, some important additions were made by my rather more tech-savvy colleague Tarinder. See if you can guess which ones.