The PCI Special Interest Group has announced another milestone in the development of PCie 6.0. Last October we heard that the PCIe 6.0 v0.3 spec was ready for members, now it has been elevated to version 0.5. The newer version is said to incorporate changes reflecting significant member feedback and marks "momentous progress," according to PCI-SIG, an organisation which doesn't usually indulge in overstatement.

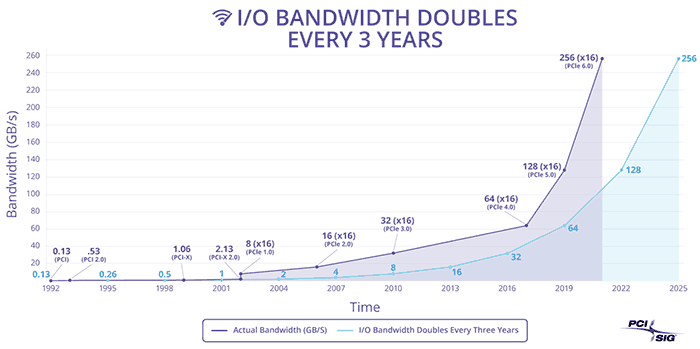

While it took a considerable seven years from the introduction of PCIe 3.0 (2010) to the PCIe 4.0 spec landed, the special interest group has found new vigour and its forward charted progress is exponential. As charted previously, the bandwidth delivered by full versions number updates to the PCIe interface specs should double every three years. The PCI-SIG asserts that it is actually ahead of that curve at the time of writing and aims for things to stay that way.

Moving from v0.3 (concept) to v0.5 (first draft), is a well practised step for the PCI-SIG and it is expected that we will see v0.7 (complete draft) next, followed by the v0.9 (final draft) which goes on to become v1.0 (final release) after internal review by member companies. Typically v0.5 "has a complete set of architectural requirements and must fully address the goals set out in the 0.3 draft."

The last chance to add functionality to the spec will be now, ahead of the publishing of v0.7. However, companies will now start developing test silicon with the 'first draft' in hand. PCIe 6.0 will be a main theme of the presentations and discussions at the PCI-SIG Developers Conference 2020, from 3rd - 4th June.

Source: PCI-SIG. Other material: AnandTech, ChipEstimate.