...and badder

Keeping the more-is-better trend going is a massive 24MB of shared L3 cache, Intel Turbo Boost technology, and four QuickPath Interconnects (QPIs) - double that of the recently-launched Xeon 5500-series. It's worth noting that the inclusion of four QPIs will result in another new and yet-to-be-named socket, but it also paves the way for Intel's QPI-connected eight-socket Boxboro-EX chipset.

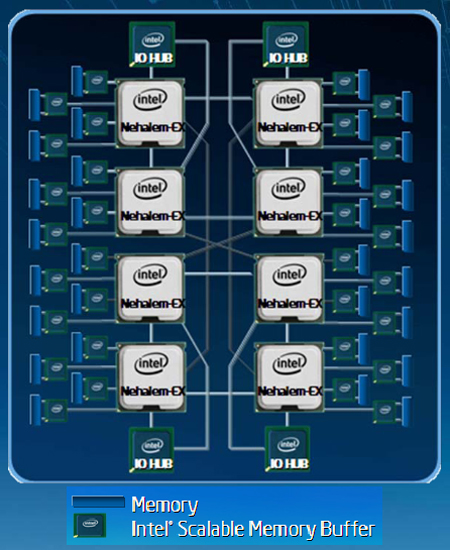

Eight sockets at 16 threads a piece provides a mind-boggling total of 128 threads. Keeping it all fed, too, shouldn't be a problem as Intel's doubling the memory capacity by supporting up to 16 DIMMs per slot - that allows, in theory, for up to 128 DIMM slots and over 1TB of installed memory. We can't see many OEMs going to such extremes, but the option's there.

New to the Nehalem-EX platform is Intel's Scalable Memory Buffers, board-mounted buffers that act as an interim between Nehalem's onboard memory controllers and the system's memory modules. Why's it significant? Well, it ensures Nehalem-EX supports standard, non-buffered memory - which in effect should help keep down costs.

Intel still isn't willing to comment on clock speeds or model names, and the vague second half of 2009 time frame leaves us all unsure of when exactly Nehalem-EX will ship. There's no doubting its performance potential, though.