Clarksboro chipset

While the previous-generation Tulsa processors used the E8501 chipset, the Caneland platform and its Tigerton CPUs work with the new 7300 chipset - also known as Clarksboro.

The number may have gone down but don't let that fool you. Intel has made some big improvements over its previous multi-processor chipsets.

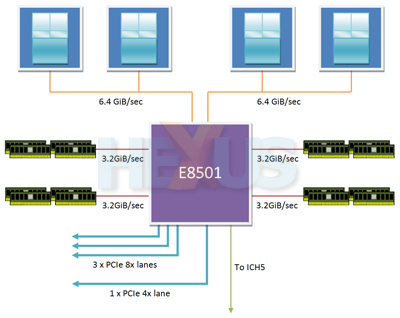

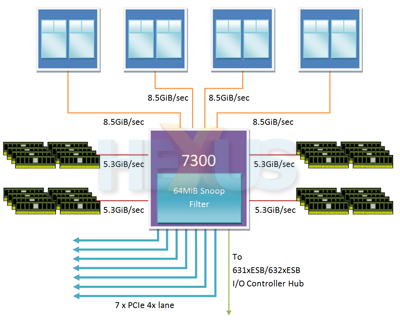

To help in the explanation, we have a pair of simplified block diagrams, offering a high-level overview of the connectivity of the E8501 and 7300 chipsets.

The older E8501 chipset is outfitted with two separate front-side busses, each interfacing with two processors. Each bus runs at a speed of either 667MHz or 800MHz, depending on the specification of the processor installed, offering a maximum bandwidth of 6.4GiB/sec to the processor pair.

Memory used with E8501 is either Registered DDR-266/333 or Registered DDR2-400, with up to four separate memory channels. With Registered DDR2-400, this gives a total of 3.2GiB/sec per channel or 12.8GiB/sec in total. Overheads aside, that puts it equal with the total front-side bus throughput. Four modules can be fitted to each channel, for a total of 16 DIMMs.

Older Tulsa CPUs were equipped with up to 16MiB of L3 cache to compensate for the shared front-side bus and the relatively low speed of the memory they were working with but such a cache is not required by Tigerton processors.

With E8501, a total of 28 PCIe lanes are present, three configured as 8x and one as 4x. Further connectivity is handled by the somewhat long-in-the tooth ICH5.

Things are rather different with the 7300 chipset, the most obvious change being to the front-side bus arrangement. Each processor now gets its own independent front-side bus and this is increased to 1066MHz across the range. As a result, each CPU has an 8.5GiB/sec link to the 7300 northbridge, alleviating one of the major potential bottlenecks seen with the E8501 design.

Additionally, while cache coherency traffic still has to traverse the front-side bus, even for separate dice on the same package, the northbridge now has a 64MiB Snoop Filter. This stores a directory of currently cached data from all the system CPUs, in an effort to reduce traffic across the front-side busses.

There's also a switch in the type of memory used - Registered DDR/DDR2 being replaced by FB-DIMMs running at 667MHz. The total number of channels remains the same, but the overall throughput increases to 5.3GiB/sec per channel - some 21.2GiB/sec in total.

Further, the 7300 supports eight DIMM devices per channel, addressing a potential maximum of 512GiB.

However, FB-DIMMs are not without their downsides. The AMB (Advanced Memory Buffer) on each device introduces additional latency and can use somewhere in the region of 10-15W. Given that at least four devices are needed for optimal performance, this power penalty can add up very quickly.

The individual front-side busses, combined with the Snoop Filter and increased memory bandwidth, are all likely to have been factors in Intel's decision not to include L3 caches on Tigerton processors. Another is that doing away with the cache reduces die size for the chips, helping improve Intel's production yields and also marginally reducing power consumption - although cache is far less power-hungry than logic circuitry.

The total number of PCIe lanes remains at 28 but these are now configured as seven 4x connections allowing for a greater number of devices to be connected.

Summary

The 7300 chipset is a big improvement over E8501 but, though new, lacks the elegance of AMD's established HyperTransport architecture and could suffer in I/O intensive applications.

Put simply, while the 7300 pushes back the limitations and bottlenecks within a four-socket Intel system, it doesn't completely eliminate them. With double the number of higher-performance cores at its disposal, compared to the previous-generation Tulsa-based systems, this may lead to performance-scaling issues.