Lots more clever stuff

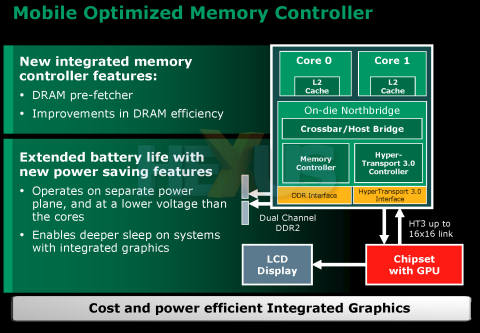

Puma will use V3 of HyperTransport - the frontside bus replacement that interconnects the processor and chipset. One of the results is said to be a significant increase in bandwidth between the CPU's on-board memory and the chipset where the integrated graphics processor resides.

AMD is also integrating 65nm CPU cores into Griffin and doubling the size of L2 caches to 1MB. Performance should be further enhanced "significantly" by a couple of other developments.

One performance boosts is promised by the use of a DRAM pre-fetcher - a piece of logic that keeps an eye on what's going on, notices a pattern developing and speculatively anticipates the next transaction, so as to reduce latency.

The other is a new memory-controller in the northbridge that's reckoned to better exploit the inherent capabilities of DRAM.

To help extend battery life, the entire northbridge works on a separate power plane to the CPU cores and at a lower voltage - an arrangement that's said to be especially beneficial on computers using integrated graphics.

With integrated graphics, there's most room for gain in the very common situation where the screen display is static. When that's the case, the display can simply be refreshed from memory and, since the CPU cores are doing no work, they can have their voltage reduced - something that's not practical when everything is sharing the same voltage-plane.

We asked whether there would be any problems resulting from latency as result of the shutdown of the CPU cores but Mr Steinman said that wouldn't be an issue because "unnatural" dependencies between different elements have been reduced - as typified by the separate voltage-planes and use of separate clocks for the northbridge and each core, rather than just a single clock.

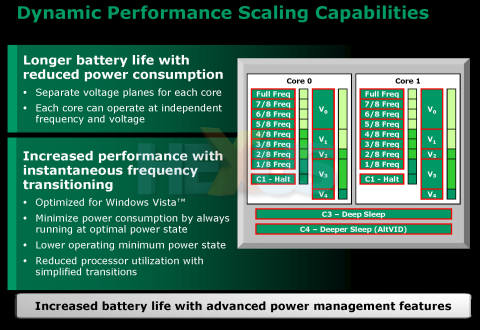

As well as having their own clocks, the cores, too, have their own independent voltage-planes - a la Barcelona. This can also produce considerable power savings, notably where one core is doing a lot less work than the other.

In a scenario where, say, one core is ripping a CD while the other is doing nothing or handling a non-intensive task, it is possible to provide different voltages to each. That's in contrast with a design that has a single voltage-plane where the core doing less works gets the same voltage as the busier one, even though it doesn't need it.

AMD also claims that its forthcoming chippery offers almost instantaneous frequency changing of the cores by digital means rather than relying on changes made by a phase-locked loop (PLL). That should greatly improve responsiveness compared with current-generation CPUs where the memory and HyperTransport have to shut down every time the PLL relocks to change frequency.

One further advantage of avoiding the usual dependency on a PLL is that it's not necessary to work around screen-flicker problems that can be caused by changes in frequency.

A PLL is still used, however, but it's locked at the CPU's maximum frequency, leaving downstream digital logic - pulse-edged modification and selection - to divide the clock as needed.

And the degree of accuracy that's possible is said to be measured in microseconds, rather milliseconds - roughly a thousand-fold improvement and in keeping with the demands that Windows Vista Premium makes.

With current-generation AMD product, cross-dependencies means that it's not possible to run at frequencies below 800MHz. The new design does away with that limitation, offering further power-saving possibilities by its ability to drop the frequency to one-eight of the CPU's stated speed.

Power-saving is also promised in a whole lot of other ways, as explained over on page four...