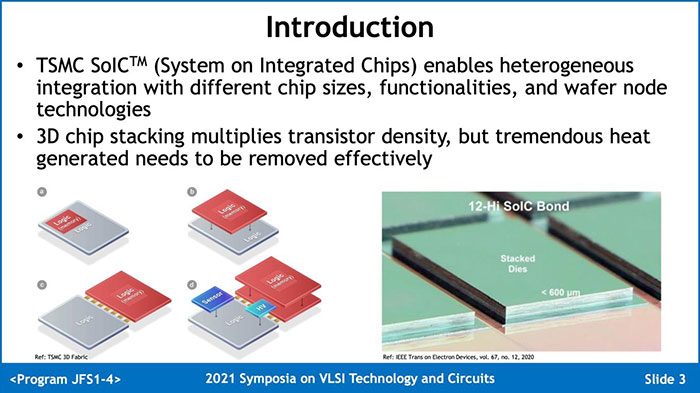

At the virtual Computex this year, AMD showcased some of its upcoming advanced technology. One of the most interesting projects that we will see in shipping products in a few months time is the use of 3D stacking of chiplets – implemented by AMD in what it calls 3D V-Cache technology.

Shortly after Computex, AMD published a video summing up the attractions of 3D V-Cache. In brief, this stacked cache on a prototype modified Ryzen 9 5900X ran modern AAA games 15 per cent faster, on average, compared to a system with the unmodified CPU. That is a big result that was precipitated thanks to the chip's improved interconnect density and also aided in energy efficiency. Production of the highest-end AMD Ryzen processor products featuring 3D chiplets is scheduled to start at the end of the year.

So far so good, but there is a looming and important drawback to 3D stacking chips that needs addressing to ensure a smooth path forward, and that is cooling. Stacked chips will be naturally more likely to suffer from the ill-effects of heat build-up within their structures than 2D architectures. HEXUS has previously reported on intrachip microchannel cooling technology (back in 2017), and now with the advent of the 3D stacked chip age, it looks like researchers at TSMC are seriously considering adopting very similar tech.

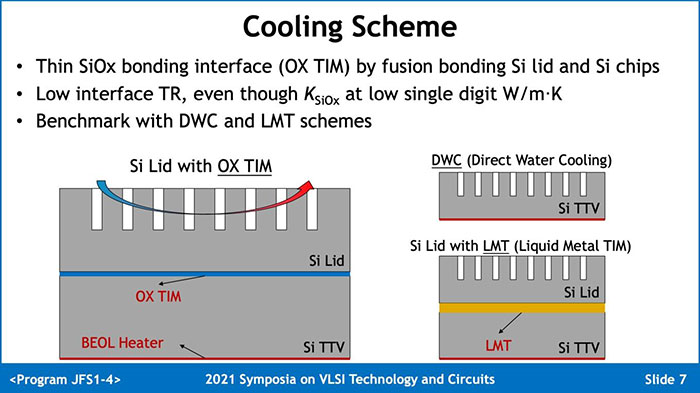

HardwareLuxx editor Andreas Schilling has written about a presentation shared by TSMC at the recent VLSI Symposium, sharing various illustrations and slides from the event. I've reproduced some of the key slides above and below. There are three main ways in which TSMC foresees intrachip cooling being applied, as follows:

- DWC (Direct Water Cooling): The channels for water cooling are incorporated directly into the top silicon layers of the chip

- Si Lid with OX TIM: The water cooling is incorporated into its own silicon layer and this in turn is brought together with the chip using an OX (Silicon Oxide Fusion) as a thermal interface material (TIM)

- Si Lid with LMT: Instead of the OX layer, liquid metal can simply be used

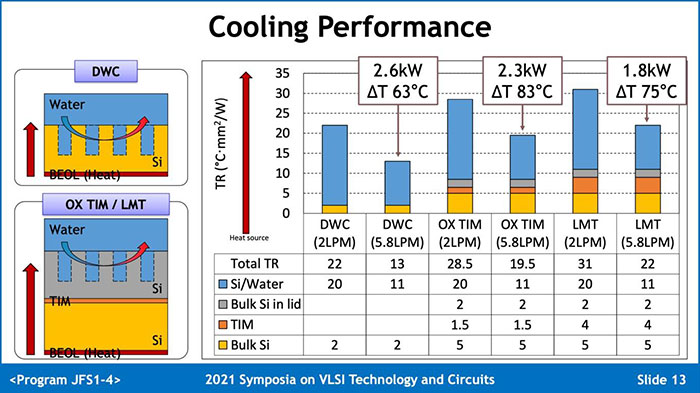

Various channelling tech was also assessed by TSMC using a heating element called a TTV (Thermal Test Vehicle) in place of a 3D stacked processor. In the chart below, you can see the test results using the three alternatives, each with two flow rates compared; 2l per minute, and 5.8l per minute.

In summary, DWC with microchannels etched directly in the processor silicon seemed to be a winner. It was found that microchannels cut in both x and y axes (square pillar) worked better than linear channels (trench). I wouldn't be surprised if some fluid physicist could work out an even better channel structure, but it might be more difficult for the machinery to cut or etch into the silicon.

It will be interesting to see which TSMC customer is the first to adopt microchannel liquid cooling. Perhaps it will become popular as 3D stacking becomes more mainstream and thermal throttling becomes more of a problem.