Nocona Xeon Basics

There's a little bit to cover in terms of Nocona's basic performance, compared to Opteron and the previous Xeon range.800MHz front side bus speed means 6.4GB/sec of bandwidth between the CPU and memory controller, for communicating with the MCH. Up from 533MHz on the older Xeon, that's a full 1.5X increase, giving an extra 50% of bandwidth.

Dual-channel DDR-II memory on the new MCH bridges that support Nocona mean that the new Xeon's front side bus speed matches the PC2-3200 memory specification in terms of bandwidth. Two channel of PC2-3200 DDR-II is 6.4GB/sec of theoretical bandwidth from the memory controller to any connected CPUs.

That brings us on nicely to the bus the Xeon rides, while connecting to the MCH. AGTL+ is a shared bus and bus protocol, where each Xeon CPU connected to the MCH is sat on the same bus link. When the CPU wishes to use the bus, it signals to the MCH and the other connected CPUs that it's going to do so, effectively locking the bus between itself and the MCH for exclusive access, before giving that access up at the end of its interaction.

This kind of shared bus, unlike Opteron which enjoys a per-CPU exclusive link between itself and its on-CPU memory controller, and an exclusive HyperTransport bus path between itself and the rest of the connected CPUs and devices that make up an Opteron system, can result in bus contention, certain types of cache contention and thrashing (since caches are somewhat shared in a multi-CPU Intel x86 system) and basic under-utilisation of the capabilities of each CPU, resulting in potential poor performance.

So the basic front side bus is faster, giving more bandwidth to the memory controller, and the memory controller itself supports faster memory, but the CPUs still ride the same old knackered shared bus that multi-CPU Intel systems have since I can remember. Opteron's point-to-point bus links are one of the key factors in its high tested performance, Intel would maybe do well to investigate a similar bus scheme for future products. Ramping up bus, memory and core clock speeds isn't the answer, since they make the AGTL+ bus look even more outdated and a means to a performance bottleneck.

The CPU itself is built on Intel's 90nm process, utilising 125 million transistors in order to create a CPU core that implements MMX, SSE/2/3, EM64T and which houses 1MB of exclusive L2 cache (L1 isn't mirrored in L2) and a 16KB L1 data cache with a 12K entry µOp trace cache for storing instruction µOps.

Package wise, the Nocona Xeon uses the same PGA603 socket (603 pins) and Pentium 4-like package incorporating an integrated heatspreader, as previous Xeon CPUs.

Finally, maximum heat output for Nocona is rated by Intel at 125W (regardless of CPU frequency), making it a toasty wee beastie, maybe largely unsuitable for blade servers and smaller 1U rack enclosures.

Pictures?

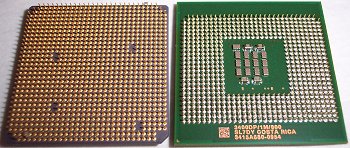

Opteron and Xeon share roughly the same physical dimensions. A smaller heatspreader adorns the Xeon, with some visible SMT components on the top of the green substrate. Weight wise, not that it's much concern, the Opteron is far heavier, due to the larger heatspreader and use of ceramic substrate for the CPU package.

940 pins versus 603. You can see the Xeon's model markings on the bottom, showing you the test CPU (CPUs, there's another hiding out of shot for some more geek porn later in the article) is a 3400DP (DP means dual processor max, the MP variant needed for systems using more than two processors) with 1MB of cache running on an 800MHz bus, made in sunny Costa Rica.

Finally, note the little hole in the top of the Xeon's heatspreader. It's designed so that the magical pixie overlords that run the CPU core can escape when things get too hot.