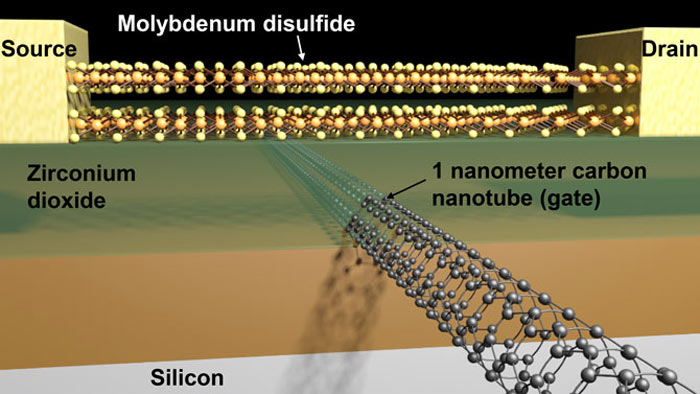

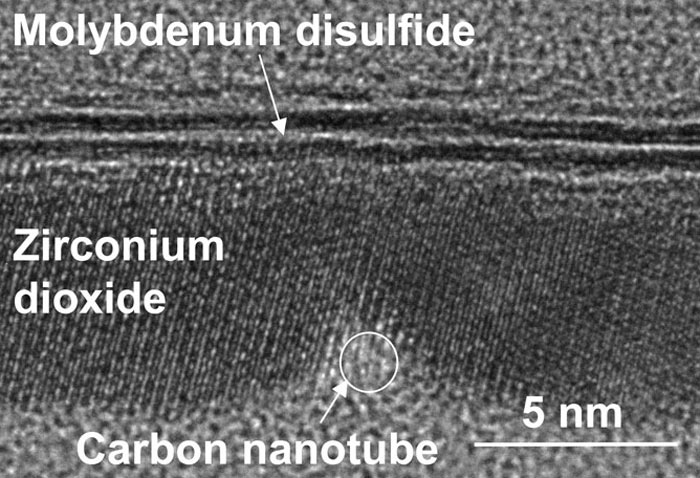

A research team at the US Department of Energy's Lawrence Berkeley National Laboratory (Berkeley Lab) has created a transistor with a working 1-nm gate. Lead by faculty scientist Ali Javey, the team says they have thus broken a "major barrier in transistor size" to create the "Smallest. Transistor. Ever."

Conventional semiconductor materials will hit a 'brick wall' at 5nm, simply down to the laws of physics, think scientists. However, thanks to the choice of cutting edge materials, the Berkeley Lab team has gained a lot more room for miniaturisation. As described by the Berkeley Lab Blog, the key to the creation of the smallest transistor ever was the use of carbon nanotubes and molybdenum disulfide (MoS2). Carbon nanotubes have been in science and tech news a lot in recent years/months with IBM, for example, describing them as the basis for our 'post-silicon future'. (IBM also saw the potential of combining these carbon structures with molybdenum.)

Berkeley Labs refers to molybdenum disulfide (MoS2), commonly used as an engine lubricant, as its other key material. While electrons travelling through Silicon gates of under 5nm would be "out of control" due to a quantum mechanical phenomenon called tunnelling, the heavier electrons in molybdenum can be controlled with these smaller gate lengths. Furthermore MoS2 can be scaled down to atomically thin sheets, of about 0.65nm thick.

As conventional lithography techniques don't scale down well to 1nm structures, researchers brought carbon into play as it can form hollow cylindrical tubes with diameters as small as 1nm (nanotubes). The MoS2 transistor with carbon-nanotube gate effectively worked as "the shortest transistor ever" assert the Berkeley Lab team.

There's still a long way to go to leverage this combination of materials to commercially construct computer chips. The research team admits their feat is just a "proof of concept". However they conclude that "this work is important to show that we are no longer limited to a 5nm gate for our transistors." The implication is that "Moore's Law can continue a while longer by proper engineering of the semiconductor material and device architecture".

Last week the world's biggest chip foundry, TSMC, spoke of its initiative to allocate as many as 400 R&D staff to 3nm process development. It said the same staff would subsequently begin R&D for 1nm manufacturing.