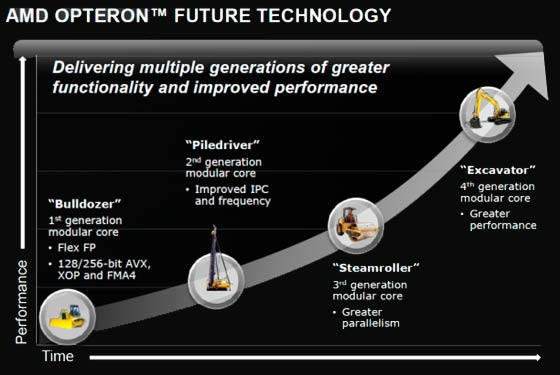

AMD’s Steamroller processor architecture has been detailed at the Hot Chips Symposium by AMD Chief Technology Officer Mark Papermaster. AMD expects Steamroller to achieve a 15 per cent performance improvement per watt over the Piledriver core. The process size will not be reduced as AMD implements Steamroller but improvements will come through design level enhancements. Steamroller will feature as the computing cores in Kaveri APUs.

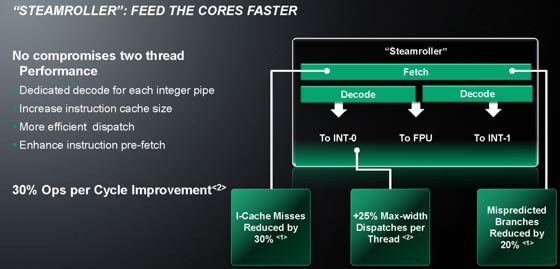

Piledriver improved upon Bulldozer by implementing FMA3 instructions for floating-point scalar and SIMD operations, and a new half-float conversion instruction, F16C, as well as offering higher CPU frequency configurations. Now Steamroller is bringing improvements mainly due to "greater parallelism" in the design which "feeds the cores faster". Importantly for road warriors Steamroller also has improvements in power consumption or performance/watt design.

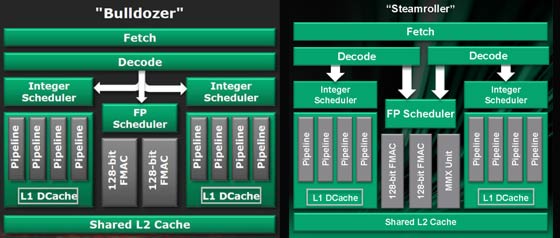

You can see from the diagrams above one of the most significant architectural changes in Steamroller from the previous Bulldozer and Piledriver cores; data can be sent to the processor cores more rapidly with a dedicated decode unit for each integer pipe which will reduce branch prediction errors by 20 per cent and cache misses by 30 per cent according to AMD.

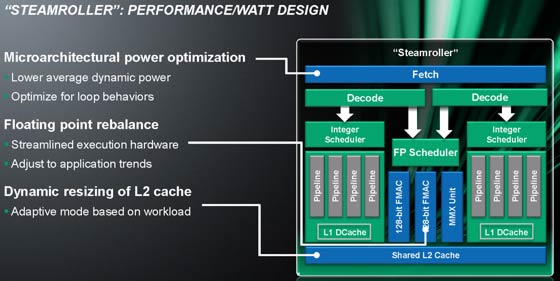

The performance/watt improvements are quite impressive. AMD have implemented a clever dynamic shared L2 caching system which can shrink to save power when running on battery, for instance. When plugged in your power management options can be set to utilise the full L2 cache.

Also AMD claim to have reaped the benefits of a process size reduction without reducing the process size! A 30 per cent reduction in layout area was implemented by using a high density cell library template for the chip design, an efficiency bringing with it a reduced power draw. Another power conscious change AMD will bring with Steamroller implementations is enhanced power management within the heterogeneous systems architecture (HSA). Dynamic clock speed adjustment of processor cores and GPU usage will be balanced to suit your computing requirements and also bring better battery life stamina to the future Steamroller equipped APUs.