Power management, ARMv8-A support

Saving each mW of power is extremely important for entry smartphones where the overarching goal is to maximize battery life.

The Cortex-A35 supports new power management capabilities that enable further power savings while making it easier for designers to integrate these features in their next-generation entry mobile SoC platforms. Highlighting three new power management features available in Cortex-A35:

- A standardized mechanism for managing device idle states using the Q-channel

- New power modes in the CPU to enable further fine-grained power savings

- Hardware support for automatic entry and exit from retention states

The combination of power management and efficiency improvements in Cortex-A35 translates into uncompromised performance at new levels of efficiency for next-generation entry mobile solutions.

The third benefit of Cortex-A35 is full support of the modern ARMv8-A architecture at unprecedented levels of efficiency. This enables Cortex-A35 based mobile devices to deliver affordable 64-bit compute by leveraging the investments in ARMv8-A software ecosystems. The Cortex-A35 is fully compatible with the vast ARMv7-A software ecosystem, and it simultaneously delivers improved 32-bit performance.

Cortex-A35 executes the A64 instruction set in the AArch64 execution state. This means that future entry mobile platforms can realise higher performance via

- Larger register banks

- Clean instruction set

- Double precision IEEE-compliant floating-point vector operations

- Native crypto instructions

In the AArch32 execution state, the Cortex-A35 runs the A32/T32 instruction sets and seamlessly executes the existing software written for ARMv7-A architecture. In addition, new crypto and floating-point instructions are also added to the AArch32 state thereby providing efficient acceleration of algorithms that use these instructions.

We discussed three benefits of the Cortex-A35 processor so far. But how will Cortex-A35 be used in future entry mobile platforms? The Cortex-A5 and Cortex-A7 have been shipping in several entry smartphone platforms using different core configurations ranging from single core to octa core.

The scalability and configurability of Cortex-A35 opens up new possibilities for ARM partners to continue innovating and differentiating for future mobile solutions while delivering the full ARMv8-A features. Cortex-A35 can be configured from an ultra low power, very small single core to four cores in a single CPU cluster.

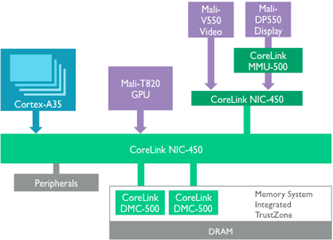

Being architecturally compatible with existing ARMv8-A processors, Cortex-A35 can also be connected as a LITTLE CPU in a big.LITTLE system. The diagram below shows one amongst several possible examples of a next-generation 64-bit capable entry mobile compute subsystem. The example uses a quad-core Cortex-A35 cluster with other energy efficient IP from ARM and is capable of delivering efficiency improvements while incorporating the premium features in affordable cost points for the next billion smartphone users.

The introduction of Cortex-A35 truly begins a new era of ultra affordable, ultra efficient 64-bit compute not just for next-generation entry mobile but also several other rapidly growing markets beyond mobile.

Efficiency is a cool thing!