Nehalem springs the shocks

Intel openly stated that its advanced 45nm process technology will be fully realised by its next-generation microarchitecture that currently goes under the name of Nehalem.

Penryn may have included no real shockers, but Nehalem does.

Whipping out the slides again:

45nm high-k metal gate

The goodness of a manufacturing process that can fit twice as many transistors into a given die space as current 65nm production and be energy-efficient at the same time, is the bedrock upon which Nehalem will be based.

It makes sense, we suppose, once you appreciate just what Intel is trying to accomplish with Nehalem.

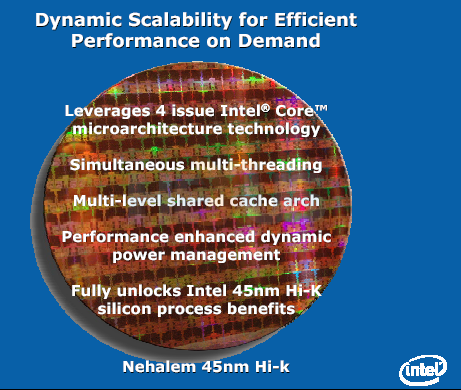

Four-issue core and SSE4

Nehalem will continue to harness the Core microarchitecture's ability to fetch, decode, execute and retire 4 instructions per clock cycle. That will offer it a 33 per cent boost when compared to competing architectures. SSE4 support, obviously, is a Nehalem feature.

Lots of cores and a return to a form of Hyper-threading

Parallelism is the way forward, and Nehalem will support up to 8 cores per physical processor. If that's not enough to get your pants wet, Intel is bringing back a form of Hyper-threading, dubbed Simultaneous multi-threading, which will be able to handle two threads per core, or, potentially, 16 threads per processor.

Intel hasn't released specifics on just how SMT is likely to be implemented, though. We're also somewhat concerned with the likely TDP of a 16-core monster, let loose with SMT-enabled rage.

Multi-level shared cache

The Penryn's cache arrangement is also being overhauled for Nehalem. Reading between the lines, it appears as if the new architecture will allow cores to completely share cache contents. Bolstering this thinking is Intel's confirmation that Nehalem will have genuinely dynamic management of individual cores, threads, caches and power states.

The next slide is where Mr. Smith quietly slipped in a bombshell or two.

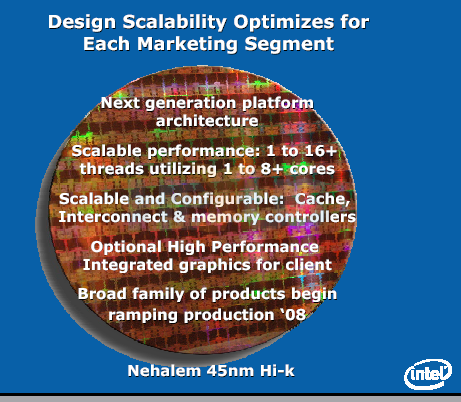

Platform architecture change

Nehalem, then, will have a potential 16 threads executing on a single processor. That level of concurrent action is sure to exploit the weakness of FSB as an efficient interconnect for a heavily multi-core system. Sure, Intel can use expensive FB-DIMMs to provide gobs of bandwidth, but the Front-Side Bus approach is a system that's just waiting to be pensioned off.

Intel's realised this and is, for want of a better word, abandoning the FSB on supporting Nehalem platforms. Rather, it will introduce a new system architecture based on a point-to-point hook-up, much in the vein of PCI-Express and HyperTransport. Exact details weren't forthcoming (CSI, perhaps?), but it appears that Intel is going down the route blazed by none other than AMD.

Integrated memory controller

Nehalem will also introduce an integrated memory controller on the processor. It doesn't take a rocket scientist to determine who has done this before, and some time ago. Again, it's a measure that makes implicit sense in a multi-core system, and, really, it should have been introduced with the Core microarchitecture. Intel will only state that the memory controller would support both buffered and unbuffered DIMMs (as it has to, considering the desktop and workstation markets it's currently supplying).

A revised interface and integrated memory controller is Intel's admittance that its present supporting architecture simply can't cut it in conjunction with a next-generation architecture. We're adamant that folks at Austin will be having a not-so-quiet chuckle to themselves. The change in architecture is sure to lead to a new socket form factor, as pin routing will require signifcant alteration, with the count likely to balloon to over 1,000.

Fusion, Nehalem, it's all the same

Back in November 2006 we highlighted AMD's plans to integrate GPUs and CPUs on to one die, brought together under the Fusion banner.

We were bullish about its prospects and could see genuine merit in amalgamating two parts of the PC jigsaw into one piece.

Intel, it seems, reckons that amalgamation is just right for Nehalem. It plans to release selected CPU SKUs with some form of integrated graphics 'fused' at the silicon level. It's got rid of the FSB, so why not throw the associated IGP in the bin while you're at it, right?

High-performance graphics are touted but we'd be surprised if this particular brand of Fusion hooked up anything hotter (in both sense of the word) than today's IGP-based graphics.

Summary

Nehalem - a lovely part of Oregon by the way - is Intel's next-generation architecture that's designed to make a clean break from the ramshackles imposed by current system architecture. The first samples are due in H1 2008 with volume shipments expected in H2, thereby beating Fusion to the integrated punch. We have little doubt that the poor enthusiast will be asked to shell out for a new motherboard, memory, and CPU form-factor again, however.Performance, predictably, should be good, yet it may become difficult to distinguish between it and AMD's offerings: both CPU companies appear to have arrived at the same design conclusion. Is Intel the new AMD, then?

HEXUS.related reading

HEXUS.net - HEXUS.reviews ::Intel Core 2 Duo/Extreme processorsHEXUS.net - HEXUS.reviews ::Intel Core 2 Quad processors

HEXUS.net - HEXUS.reviews ::Intel's Conroe spanks AMD FX-62's botty - for real!!

HEXUS.net - HEXUS.articles :: Intel's technology branding

HEXUS.net - HEXUS.reviews ::AMD's '4x4' Quad-FX platform unveiled and benchmarked

HEXUS.net - HEXUS.reviews ::AMD QuadFX pushed to the limit... and beyond

HEXUS.net - HEXUS.reviews ::AMD Athlon 64 X2 6000+ processor