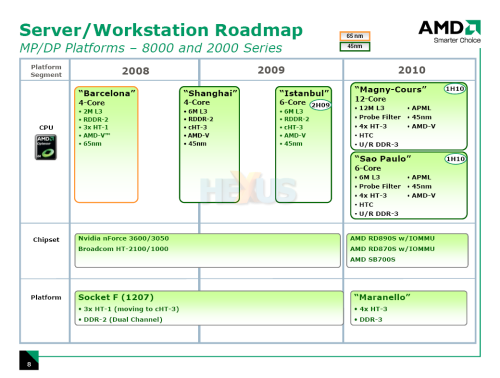

The MP roadmap

AMD disclosed its updated server roadmap during a conference call yesterday, and we covered the salient points in our analysis yesterday.Let's take a look in a little more detail now, however.

A number of points to raise here. The last 12 months has seen AMD play its cards close to its chest, divulging little in the way of future processors' existence and architecture(s). Rather, it's tended to promulgate a quarter-by-quarter approach.

Now, the roadmap is more akin to Intel's, where 30-month-long timelines are unequivocally stated. Before we get to the meat of the disclosures, the question is whether AMD can stick to it, or will it stray off the stated path? At least we have a frame of reference.

We know all about the incumbent Barcelona (Opteron) quad-core architecture. Now, finally, it's shipping, in relative volume, to partners, in B3 form. We've stated that AMD will need to release higher-clocked models to better-compete with Intel's Xeon (Harpertown) line, and it has the next six months to do precisely that.

Quad-core Shanghai is the natural successor to Barcelona. Based on 45nm technology, Shanghai can be thought of as Barcelona with benefits. The core won't change much, but additional on-chip L3 cache, better virtualisation performance, and a slew of minor performance-oriented additions should increase clock-for-clock performance by up-to 20 per cent when compared with Opteron in its Barcelona form. Shanghai, too, will fit into the same platform, Socket F, and will utilise DDR2, rather than DDR3 that was mooted some months' ago.

The Shanghai K10 variant will do battle with both the 45nm Intel Harpertown Xeon, based on the present Penryn core, and the upcoming Nehalem microarchitecture, also based on the 45nm process, but featuring an AMD-like integrated memory controller, monolithic die, smarter cache, and QuickPath Interconnects.

Moving on to mid-to-late 2009, AMD is hoping to introduce the monolithic-die Istanbul Opteron - a six-core model that's designed for 2P (and above) systems. Specifications suggest that it will be based on the Shanghai core, albeit with more per-socket power. Think of it as a partial answer to the currently-unavailable Intel Dunnington core. Again, Istanbul should be a drop-in upgrade to a Socket-F platform, and note that DDR3 is conspicuous by its absence.

A move to a new platform, Maranello (Socket G34), will take place in 2010, with six- and 12-core CPUs on the horizon. Each iteration will feature four HyperTransport 3.0 links, be based on the 45nm process, and will support DDR3 right off the bat.

The 12-core Magny-Cours SKU is an interesting model. It appears as a doubling of Sao Paulo, intimating a multi-chip module (MCM) approach. The roadmap also makes no mention of eight-core Opteron CPUs, which is interesting in itself. We know that server CPUs form the basis of desktop parts, released a little later, so, perhaps, AMD's 'Montreal' may not see the light of day.

Looking at it as a whole, AMD will need to do battle with core-scalable Nehalem architecture that Intel will bring to the table in late 2008 and then against the all-new, 32nm-based Sandy Bridge microarchitecture in 2009/2010. The roadmap doesn't suggest that AMD has quite the necessary gumption to do, if it can stick to this 'map.

We were expecting AMD to announce scant details on the grounds-up 'Bulldozer' microarchitecture, to be introduced around 2010. Given this roadmap, it seems as if it's K10 derivation for a while longer...