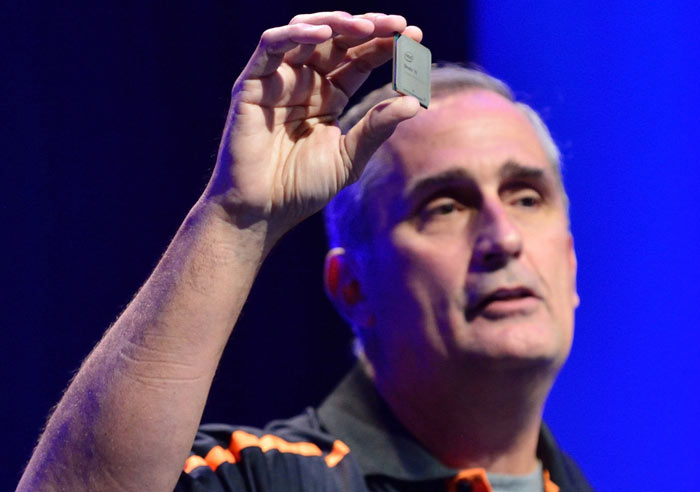

Intel has announced that it has started sampling Stratix 10 field programmable arrays (FPGA chips) to customers. The chip is significant as "the industry’s first 14nm FPGA," but not only that - it is based upon a quad-core ARM Cortex-A53 processor with integrated HBM2 in-package, using Intel HyperFlex architecture. At IDF16, Intel CEO Brian Krzanich described the Stratix 10 as "a beast," in reference to its performance and density.

It is boldly claimed that the Stratix 10 "will revolutionize the performance of data centres and networking infrastructures". The new FPGA is expected to enable service providers, data centres, cloud computing and storage systems "to satisfy their insatiable demand for higher computational capabilities, lower latency, greater system flexibility and increased power efficiencies".

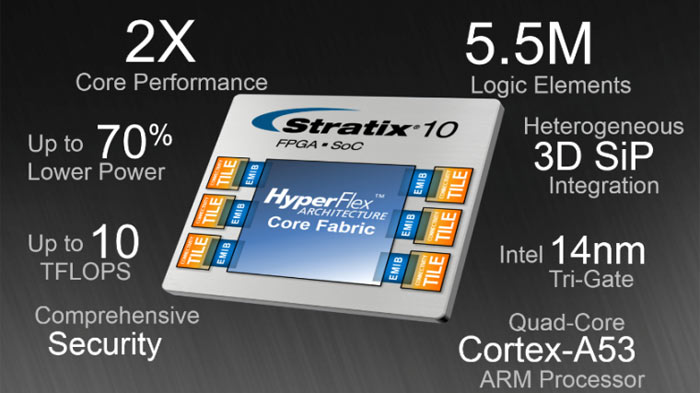

Intel broke down the advances and appeal of the new Stratix 10 into handy bullet-point chunks as follows:

- 2X the core performance and over 5X the density compared to the previous generation.

- Up to 70 per cent lower power than Stratix V FPGAs for equivalent performance.

- Up to 10TFLOPS of single-precision floating point DSP performance.

- Up to 1TBps memory bandwidth with integrated High-Bandwidth Memory (HBM2) in-package.

- Embedded quad-core 64-bit ARM Cortex-A53 processor.

FPGAs could be of particular utility value in the data centre, thinks Intel. Their ability to be "reconfigured in milliseconds to accelerate individual tasks," can provide significant improvements in performance and power efficiency over new and changing workloads. In bandwidth-intensive applications, such as delivering triple-play traffic, Stratix 10 FPGAs can enable an efficient, bandwidth-rich infrastructure.

For further detailed information on the Stratix 10 you can download the white paper (PDF), and/or watch the Introducing Stratix 10 FPGAs and SoCs, and the Stratix 10 Architecture videos.